# THE 8051 ARCHITECTURE By Dr. Naveen B

Saturday, May 1, 2021

## **Contents:**

- Introduction

- Architecture

- 8051 Microcontroller Hardware

- Pin Description of the 8051

- Registers

- Memory mapping in 8051

- 8051 Flag bits and the PSW register

- Stack in the 8051

- I/O pins, ports & circuits

- Timers & Counters

- Serial Data I/O

- Interrupts

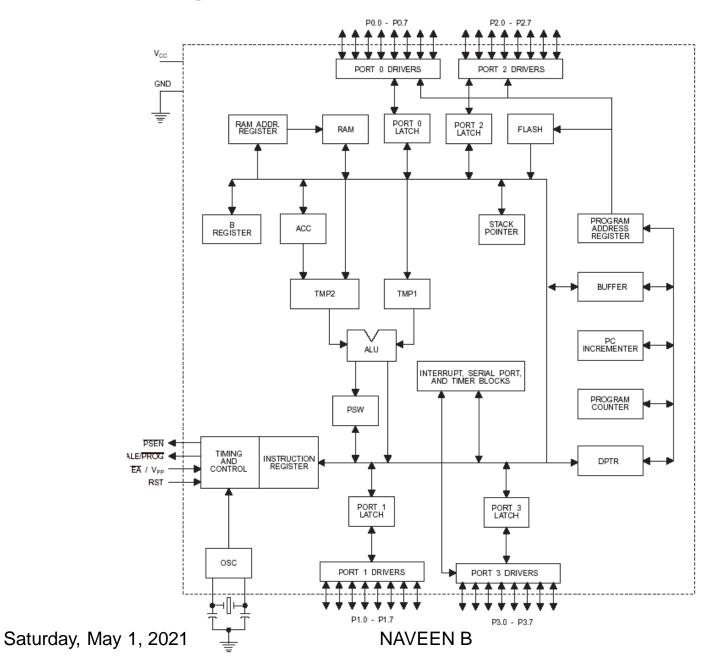

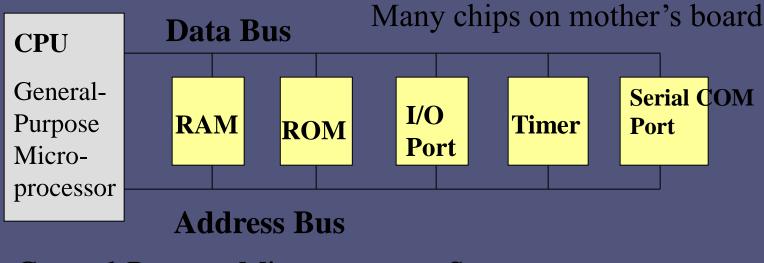

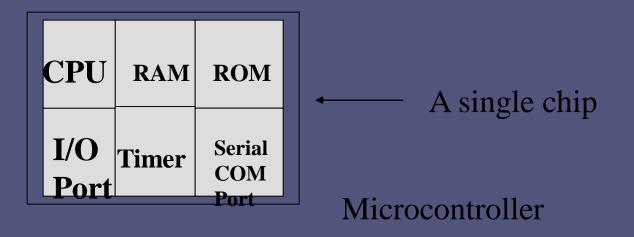

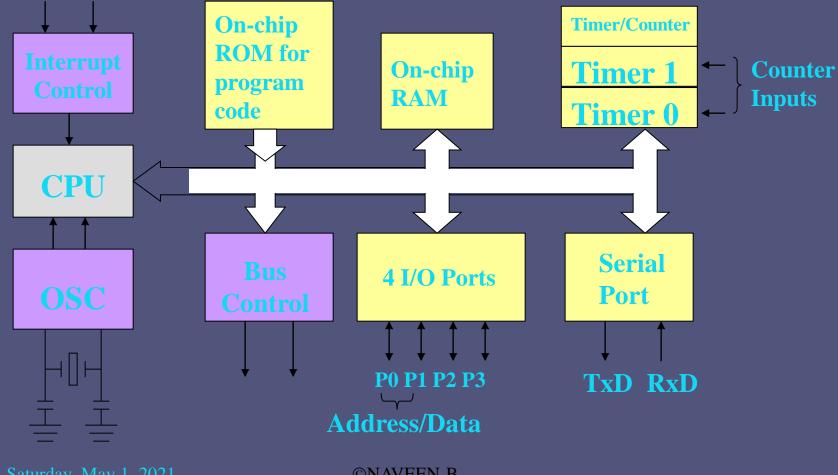

## 8051 features

- 8 bit CPU with reg. A & B

- 16 bit PC & Data pointer (DPTR)

- 8 bit PSW, 8 bit SP, onchip oscillator & clock circuits

- 64k ROM, in which 4K is on-chip, full duplex serial SBUF

- External RAM of 64K bytes & Internal RAM of 128 bytes :

- 4 reg. banks each containing 8 registers

- 80 bytes of general purpose data memory

- -16 bytes which may be addressed at the bit level

- 32 I/O pins arranged as 4 ports

- Two 16 bit timer counters, T0 & T1

- 2 external & 3 internal interrupt sources

- Control registers: TCON, TMOD, SCON, PCON, IP, IE Saturday, May 1, 2021 NAVEEN B

Block Diagram

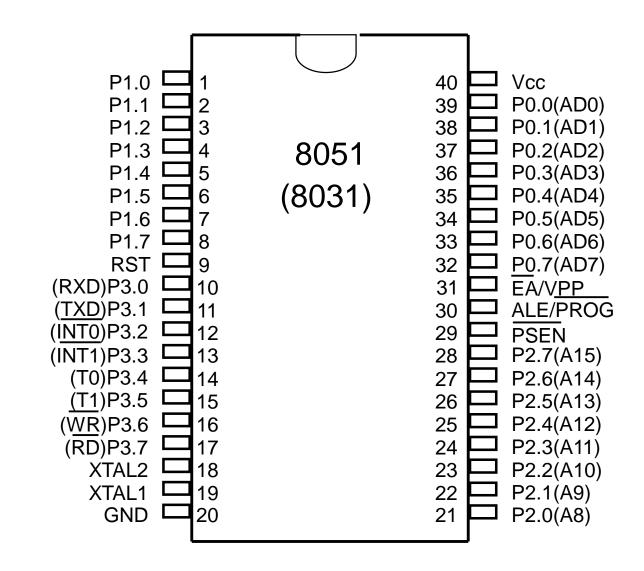

## **Pin Description of the 8051**

## Pins of 8051 (1/4)

- Vcc (pin 40) :

- Vcc provides supply voltage to the chip.

- The voltage source is +5V.

- GND (pin 20) : ground

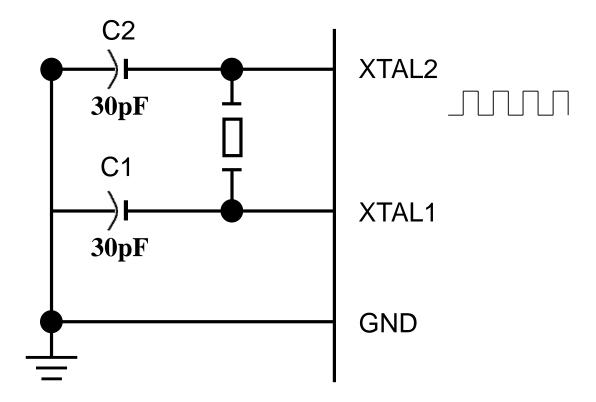

- XTAL1 and XTAL2 (pins 19,18) :

- These 2 pins provide external clock.

- − Way 1 : using a quartz crystal oscillator **I**

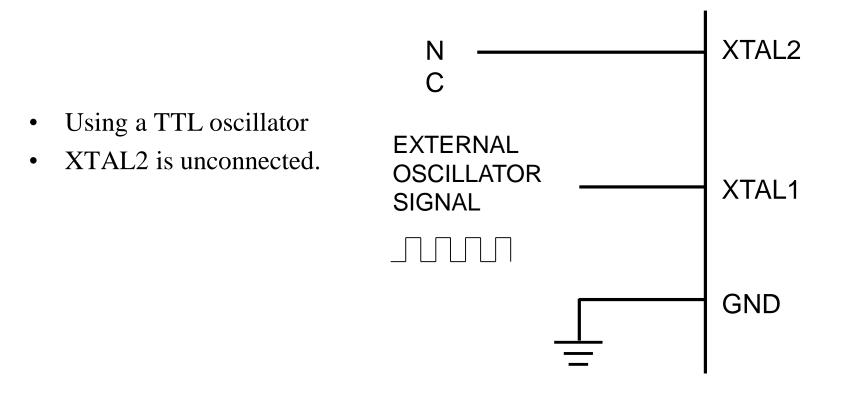

- − Way 2 ∶ using a TTL oscillator 🖬

## Pins of 8051 (2/4)

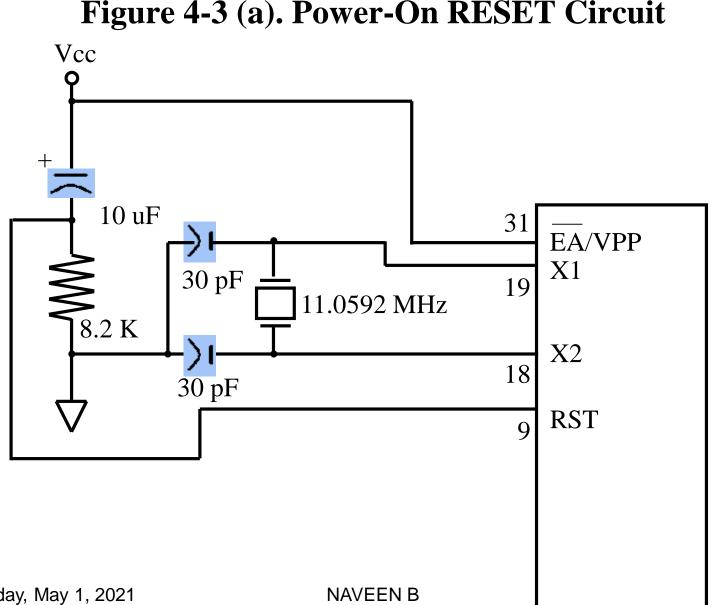

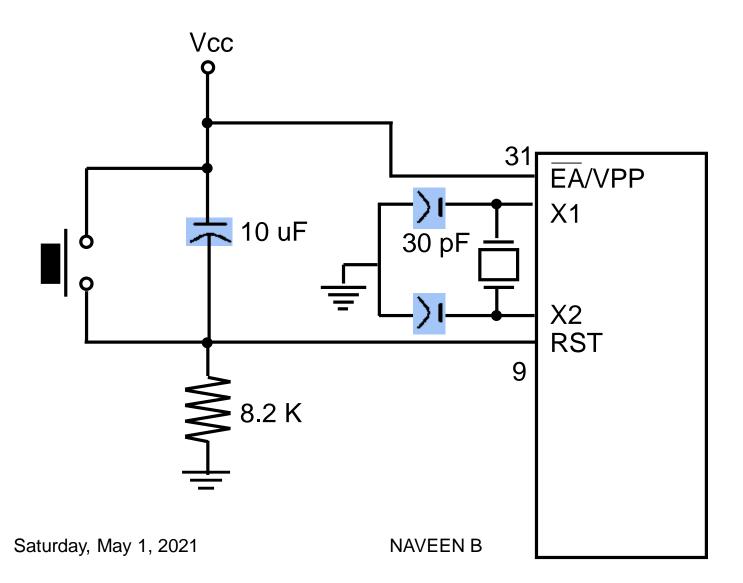

- RST (pin 9) : reset

- It is an input pin and is active high (normally low) .

- The high pulse must be high at least 2 machine cycles.

- It is a power-on reset.

- Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost.

- Reset values of some 8051 registers 🖬

- − Way 1 : Power-on reset circuit

- Way 2 : Power-on reset with debounce  $\blacksquare$

## Pins of 8051 (3/4)

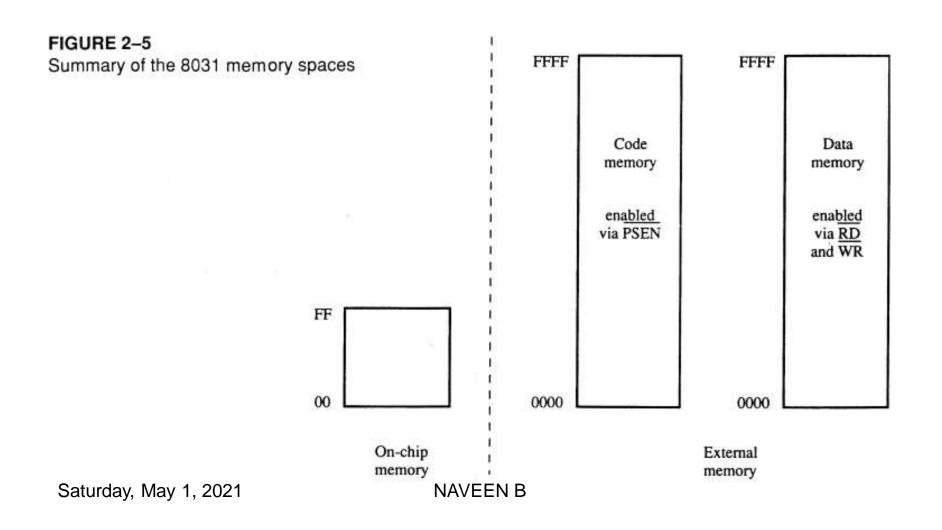

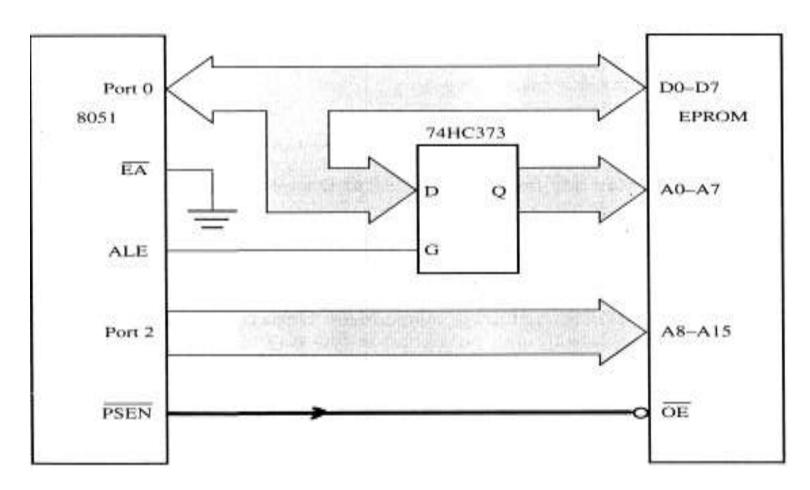

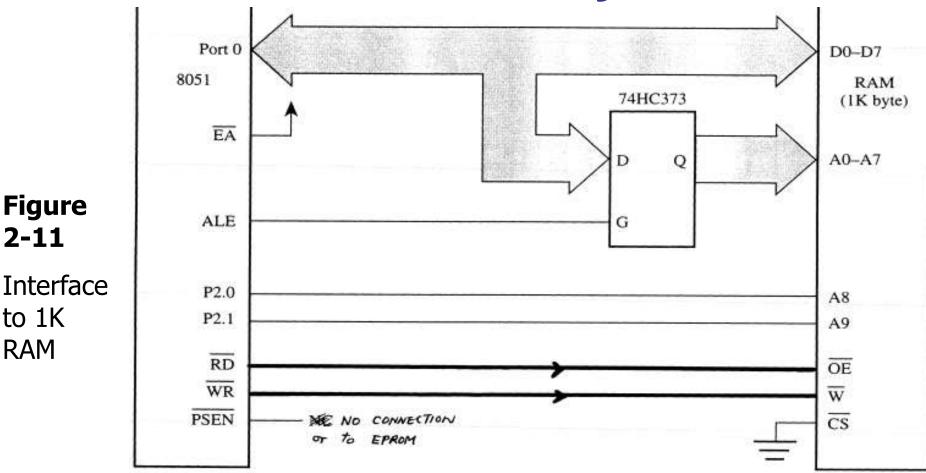

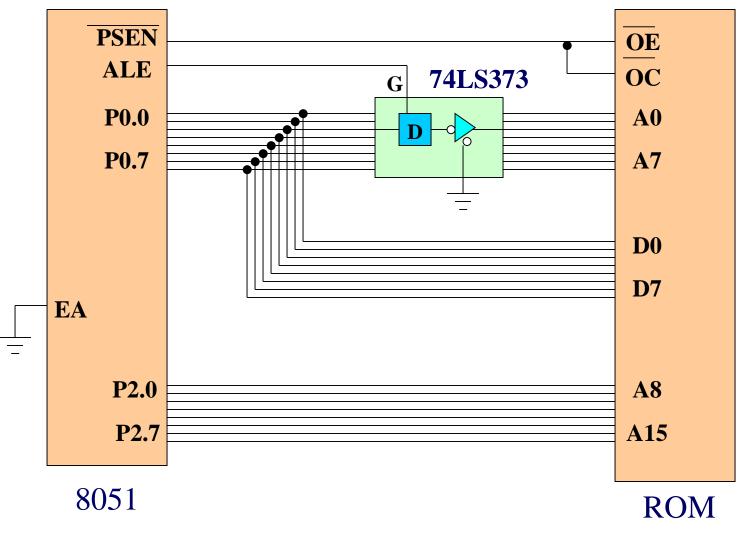

- /EA (pin 31) : external access

- There is no on-chip ROM in 8031 and 8032.

- The /EA pin is connected to GND to indicate the code is stored externally.

- For 8051, /EA pin is connected to Vcc.

- "/" means active low.

- /PSEN (pin 29) : program store enable

- This is an output pin and is connected to the OE pin of the ROM.

## Pins of 8051 (4/4)

- ALE (pin 30) : address latch enable

- It is an output pin and is active high.

- 8051 port 0 provides both address and data.

- The ALE pin is used for de-multiplexing the address and data by connecting to the G pin of the 74LS373 latch.

- /PSEN & ALE are used for external ROM.

- I/O port pins

- The four ports P0, P1, P2, and P3.

- Each port uses 8 pins.

- All I/O pins are bi-directional.

Saturday, May 1, 2021

### Figure 4-2 (a). XTAL Connection to 8051

- Using a quartz crystal oscillator

- We can observe the frequency on the XTAL2 pin.

### Figure 4-2 (b). XTAL Connection to an External Clock Source

#### **RESET Value of Some 8051 Registers:**

| Register | Reset Value |

|----------|-------------|

| PC       | 0000        |

| ACC      | 0000        |

| В        | 0000        |

| PSW      | 0000        |

| SP       | 0007        |

| DPTR     | 0000        |

### RAM are all zero.

Saturday, May 1, 2021

Saturday, May 1, 2021

### Figure 4-3 (b). Power-On RESET with Debounce

$\mathbf{X}$

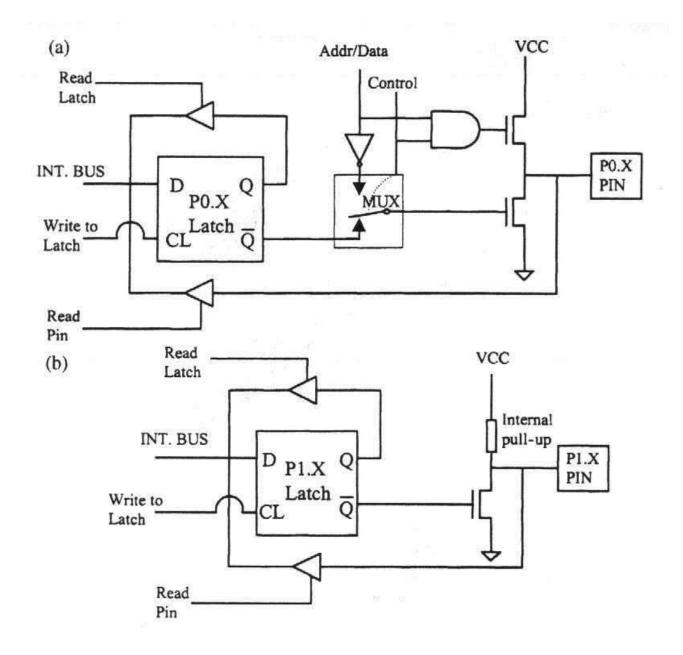

### **Pins of I/O Port**

- The 8051 has four I/O ports

- Port 0 (pins 32-39) : P0 (P0.0~P0.7)

- Port 1 (pins 1-8) : P1 (P1.0~P1.7)

- Port 2 (pins 21-28) : P2 (P2.0~P2.7)

- Port 3 (pins 10-17) ∶ P3 (P3.0~P3.7)

- Each port has 8 pins.

- Named P0.X (X=0,1,...,7), P1.X, P2.X, P3.X

- Ex : P0.0 is the bit 0 (LSB) of P0

- Ex : P0.7 is the bit 7 (MSB) of P0

- These 8 bits form a byte.

- Each port can be used as input or output (bi-direction).

$\left| \times \right\rangle$

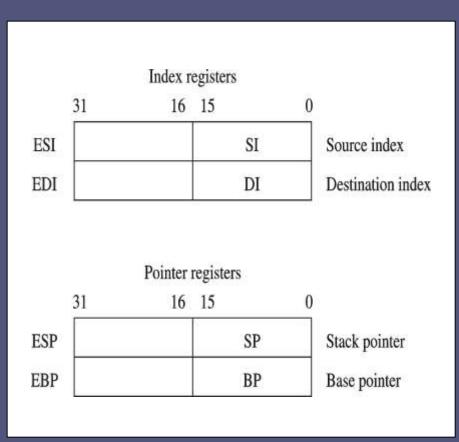

## Totally 34 GPRs ie. A & B registers along with 4 banks – each bank has 8 registers: R0 – R7. Other registers are PC, DPTR & SP

| А  |      |                         |     |

|----|------|-------------------------|-----|

| В  |      |                         |     |

| R0 | DPTR | DPH                     | DPL |

| R1 |      |                         |     |

| R2 | PC   | P                       | С   |

| R3 |      |                         |     |

| R4 |      | Some 8051 16-bit Regist | ter |

| R5 |      |                         |     |

| R6 |      |                         |     |

| R7 |      |                         |     |

Some 8-bit Registers of the 8051

Saturday, May 1, 2021

## A and B registers

- Holds the results of math & logical operations

- ' A' register is also used for data transfers between 8051

& any external memory

- 'B' register is used with 'A' register for multiplication & division operations.

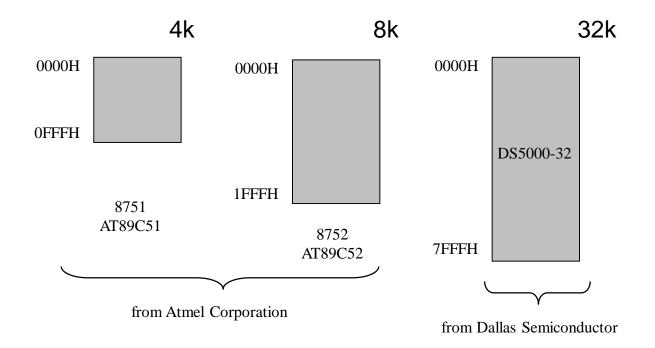

## Memory mapping in 8051

• ROM memory map in 8051 family

Saturday, May 1, 2021

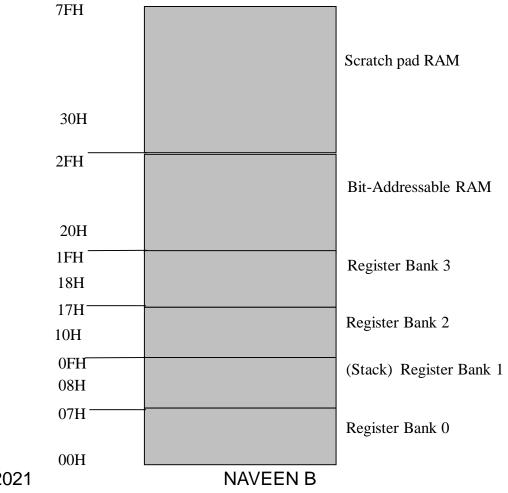

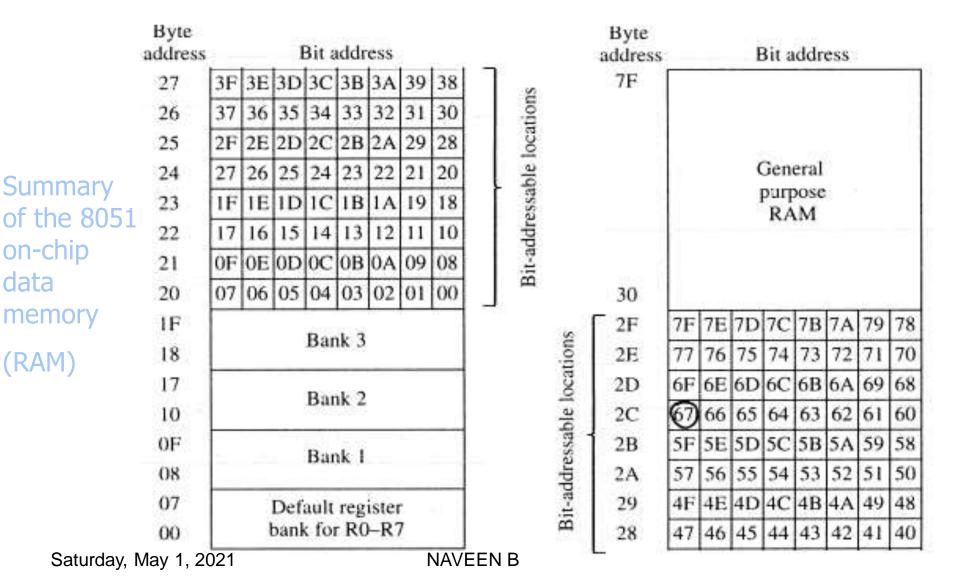

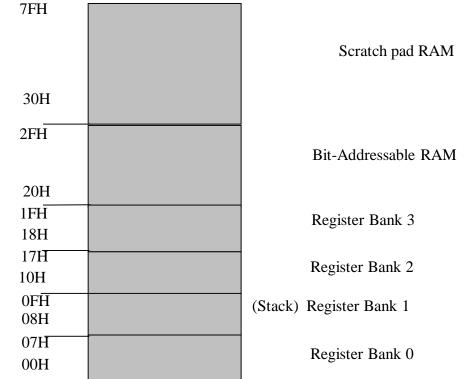

#### RAM memory space allocation in the 8051

Saturday, May 1, 2021

### A Quick Review of USER's space.....

- 00 1F : 4 Banks x 8 = 32 registers

- ONE bank at a time (RS1-RS0)

- 20 2F: 16 more locations = 16 Bytes

- Also BIT addressable (00-7F address for the 128 bits)

- 30 7F Scratch Pad (Store-Read-Write-Modify data)

- General Purpose RAM (80 bytes)

- 80 FF : Special Purpose CPU Area

- Also Contains the SFRs

# **Memory Space**

## **Bit Addressable RAM**

#### RAM

## **Bit Addressable RAM** (Special Function Registers)

|             | Byte<br>address | Bit address             |      | Byte<br>address | Bit address                |

|-------------|-----------------|-------------------------|------|-----------------|----------------------------|

|             | 98              | 9F 9E 9D 9C 9B 9A 99 98 | SCON | FF              |                            |

|             |                 |                         |      | F0              | F7 F6 F5 F4 F3 F2 F1 F0 B  |

| _           | 90              | 97 96 95 94 93 92 91 90 | P1   |                 |                            |

| Summary     |                 |                         |      | E0              | E7 E6 E5 E4 E3 E2 E1 E0 AC |

| of the 8051 | 8D              | not bit addressable     | THI  |                 |                            |

| on-chip     | 8C              | not bit addressable     | TH0  | D0              | D7 D6 D5 D4 D3 D2 - D0 PS  |

| data        | 8B              | not bit addressable     | TLI  |                 |                            |

|             | 8A              | not bit addressable     | TL0  | <b>B</b> 8      | BC BB BA B9 B8 IP          |

| memory      | 89              | not bit addressable     | TMOD |                 |                            |

|             | 88              | 8F 8E 8D 8C 8B 8A 89 88 | TCON | B0              | B7 B6 B5 B4 B3 B2 B1 B0 P3 |

|             | 87              | not bit addressable     | PCON |                 |                            |

|             |                 |                         |      | A8              | AF ACABAAA9A8 IE           |

|             | 83              | not bit addressable     | DPH  |                 |                            |

|             | 82              | not bit addressable     | DPL  | A0              | A7 A6 A5 A4 A3 A2 A1 A0 P2 |

|             | 81              | not bit addressable     | SP   |                 |                            |

|             | 80              | 87 86 85 84 83 82 81 80 | PO   | 99              | not bit addressable SB     |

Saturday, May 1, 2021

# **Register Banks**

- Four banks of 8 bit-sized registers, RO to R7

- Addresses are :

| 18 - 1F | for bank 3           |

|---------|----------------------|

| 10 - 17 | for bank 2           |

| 08 - 0F | for bank 1           |

| 00 - 07 | for bank 0 (default) |

- Active bank selected by bits [RS1, RS0] in PSW.

- Permits fast "context switching" in interrupt service routines (ISR).

Saturday, May 1, 2021

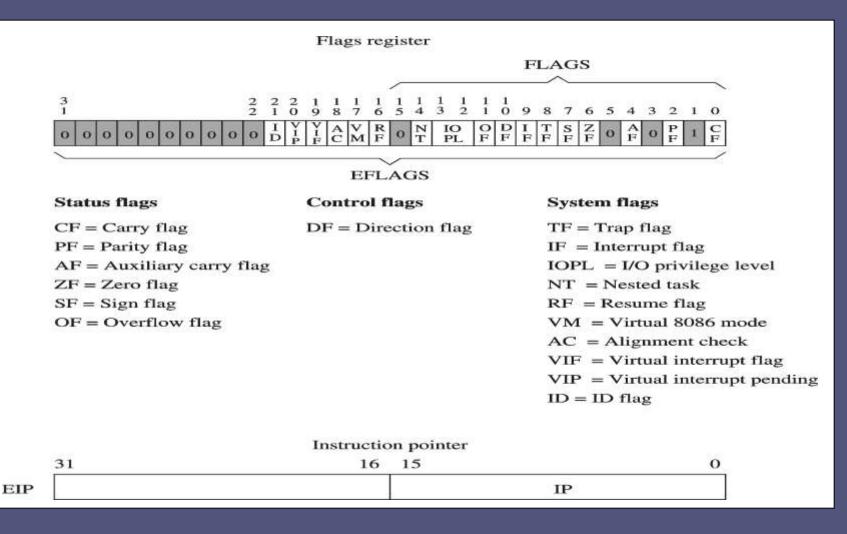

# **Program Status Word (PSW)**

#### TABLE 2-3

PSW (program status word) register summary

| віт   | SYMBOL | ADDRESS | BIT<br>DESCRIPTION          |

|-------|--------|---------|-----------------------------|

| PSW.7 | CY     | D7H     | Carry flag                  |

| PSW.6 | AC     | D6H     | Auxiliary carry flag        |

| PSW.5 | FO     | D5H     | Flag 0                      |

| PSW.4 | RS1    | D4H     | Register bank select 1      |

| PSW.3 | RS0    | D3H     | Register bank select 0      |

|       |        |         | 00 = bank 0; addresses 00H- |

|       |        |         | 01 = bank 1; addresses 08H- |

|       |        |         | 10 = bank 2; addresses 10H- |

|       |        |         | 11 = bank 3; addresses 18H- |

| PSW.2 | OV     | D2H     | Overflow flag               |

| PSW.1 |        | D1H     | Reserved                    |

| PSW.0 | P      | DOH     | Even parity flag            |

## 8051 Flag bits and the PSW register

#### • PSW Register

| CY                                    | AC     | F0              | RS1           | RS0           | OV |     | Р           | ]   |

|---------------------------------------|--------|-----------------|---------------|---------------|----|-----|-------------|-----|

|                                       |        |                 |               |               |    |     |             |     |

|                                       |        |                 |               | Carry flag    |    | PSW | 7.7         | CY  |

|                                       |        |                 | Auxiliar      | y carry flag  |    | PSW | <i>V</i> .6 | AC  |

|                                       | $A\nu$ | vailable to the | user for gene | eral purpose  |    | PSW | 7.5         |     |

|                                       |        | Re              | gister Bank s | elector bit 1 |    | PSW | /.4 ]       | RS1 |

|                                       |        | Re              | gister Bank s | elector bit 0 |    | PSW | /.3         | RS0 |

|                                       |        |                 | 0             | verflow flag  |    | PSW | <i>V</i> .2 | OV  |

|                                       |        |                 | Us            | er define bit |    | PSW | 7.1         |     |

| Parity flag Set/Reset odd/even parity |        |                 |               |               |    | PSW | 7.0         | Р   |

## For odd Parity, P=1,

| RS1 | RS0 | Register Bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00H-07H |

| 0   | 1   | 1             | 08H-0FH |

| 1   | 0   | 2             | 10H-17H |

| 1   | 1   | 3             | 18H-1FH |

Saturday, May 1, 2021

#### Instructions that Affect Flag Bits:

| Instructions | CY | ov | AC |

|--------------|----|----|----|

| ADD          | X  | Х  | X  |

| ADDC         | x  | х  | X  |

| SUBB         | x  | х  | X  |

| MUL          | 0  | х  |    |

| DIV          | 0  | х  |    |

| DA           | x  |    |    |

| RRC          | x  |    |    |

| RLC          | x  |    |    |

| SETB C       | 1  |    |    |

| CLR C        | 0  |    |    |

| ANL C,bit    | x  |    |    |

| ANL C,/bit   | x  |    |    |

| ORL C,bit    | x  |    |    |

| MOV C,bit    | x  |    |    |

| CJNE         | Х  |    |    |

Note: X can be 0 or 1

Saturday, May 1, 2021

| Example:<br>MOV A,#88H<br>ADD A,#93H |                        |                       |                        |                             |      |

|--------------------------------------|------------------------|-----------------------|------------------------|-----------------------------|------|

| 88<br>+93                            | 10001000<br>+10010011  |                       |                        |                             |      |

| 11B<br>CY=1 AC=0                     | 10 0011011<br>P=0 OV=1 | Example<br>MOV<br>ADD | e:<br>A,#9CH<br>A,#64H |                             |      |

| Example:<br>MOV A,#38H               |                        | 9C<br>+64<br>         | _                      | 1001 <sup>2</sup><br>+01100 | 0100 |

| ADD A,#2FH                           |                        | 100                   | )                      | 1 0000                      | 0000 |

| 38<br>+2F                            | 00111000<br>+00101111  | CY=1                  | AC=1                   | P=0                         | OV=0 |

| 67<br>CY=0 AC=1                      | 01100111<br>P=1 OV=0   |                       |                        |                             |      |

Saturday, May 1, 2021

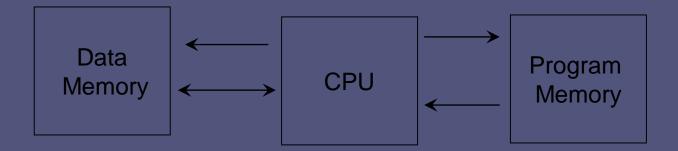

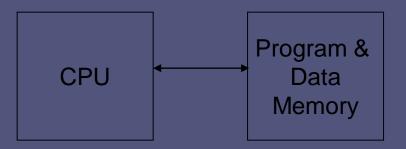

# Accessing External Code Memory

Saturday, May 1, 2021

# Accessing External Data Memory

Saturday, May 1, 2021

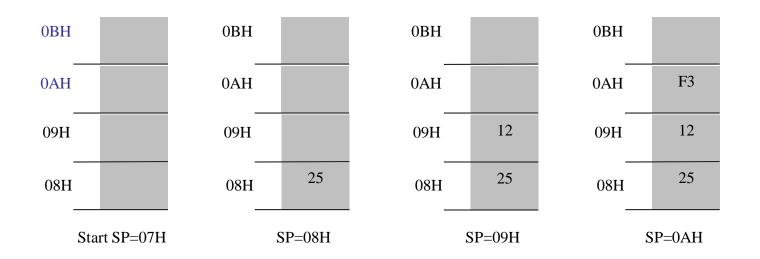

## **Stack in the 8051**

- The register used to access the stack is called **SP** (stack pointer) register.

- The stack pointer in the 8051 is only 8 bits wide, which means that it can take value 00 to 7FH.

- <u>When 8051 powered up, the</u> <u>SP register contains value</u> <u>07.</u>

#### Example:

| MOV<br>MOV   | R6,#25H<br>R1,#12H |

|--------------|--------------------|

| MOV          | R4,#0F3H           |

|              |                    |

| PUSH         | 6                  |

| PUSH<br>PUSH | 6<br>1             |

### **\*Operand is 8 bit & Direct addressing only**

Saturday, May 1, 2021

## PC (Program Counter)

- 16 bit registers used to hold the address of a byte in memory

- Program instructions are fetched by PC

- On chip ROM addresses 0000h to 0FFFh & external addresses that exceed 0FFFh

- PC is the only reg. that does not have Internal address.

## DPTR (Data pointer)

- Two 8 bit regs. DPH & DPL

- Used to furnish memory addresses for internal & external code and external Data access.

- DPTR does not have a single internal address

- DPH & DPL each assigned a address Saturday, May 1, 2021

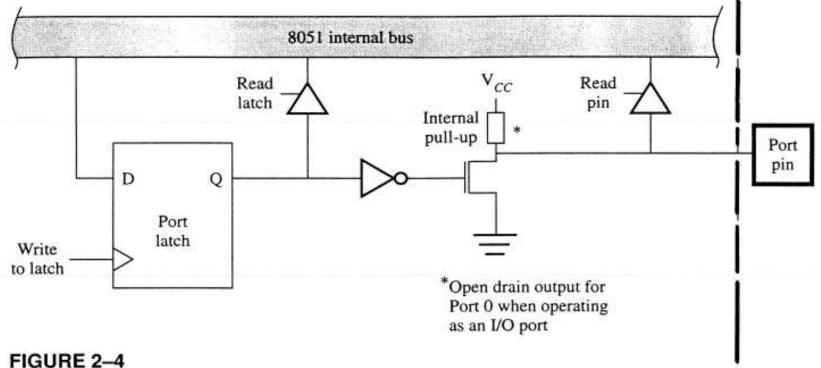

# **I/O Port Circuitry**

HARDWARE SUMMARY

Circuitry for I/O ports

Saturday, May 1, 2021

Saturday, May 1, 2021

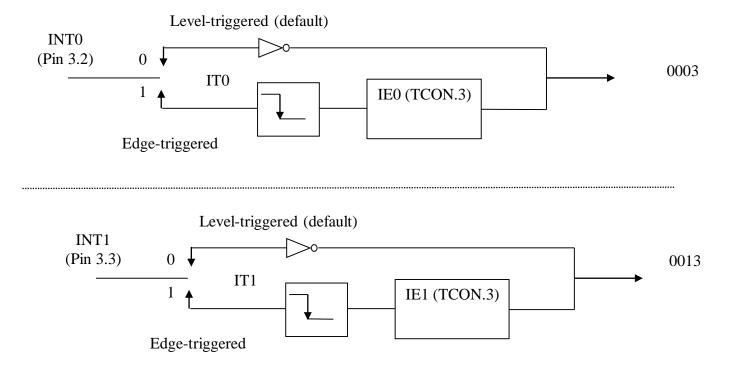

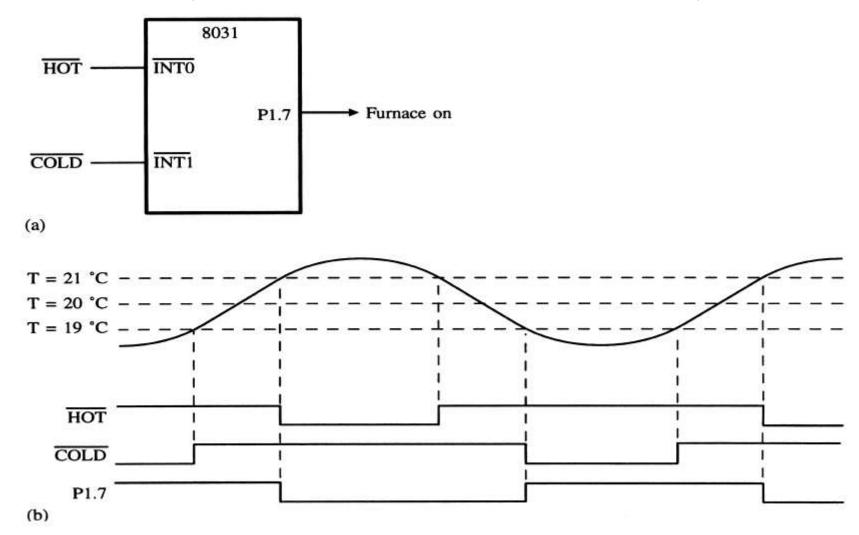

# **Alternate Pin-functions**

TABLE 2–2

Alternate pin functions for port pins

| віт  | NAME | BIT<br>ADDRESS | ALTERNATE FUNCTION                |

|------|------|----------------|-----------------------------------|

| P3.0 | RXD  | BOH            | Receive data for serial port      |

| P3.1 | TXD  | B1H            | Transmit data for serial port     |

| P3.2 | INTO | B2H            | External interrupt 0              |

| P3.3 | INT1 | B3H            | External interrupt 1              |

| P3.4 | то   | B4H            | Timer/counter 0 external input    |

| P3.5 | T1   | B5H            | Timer/counter 1 external input    |

| P3.6 | WR   | B6H            | External data memory write strobe |

| P3.7 | RD   | B7H            | External data memory read strobe  |

| P1.0 | T2   | 90H            | Timer/counter 2 external input    |

| P1.1 | T2EX | 91H            | Timer/counter 2 capture/reload    |

# **I/O Port Programming**

$\boxtimes$

### Port 1 (pins 1-8)

- Port 1 is denoted by P1.

- P1.0 ~ P1.7

- We use P1 as examples to show the operations on ports.

- P1 as an output port (i.e., write CPU data to the external pin)

- P1 as an input port (i.e., read pin data into CPU bus)

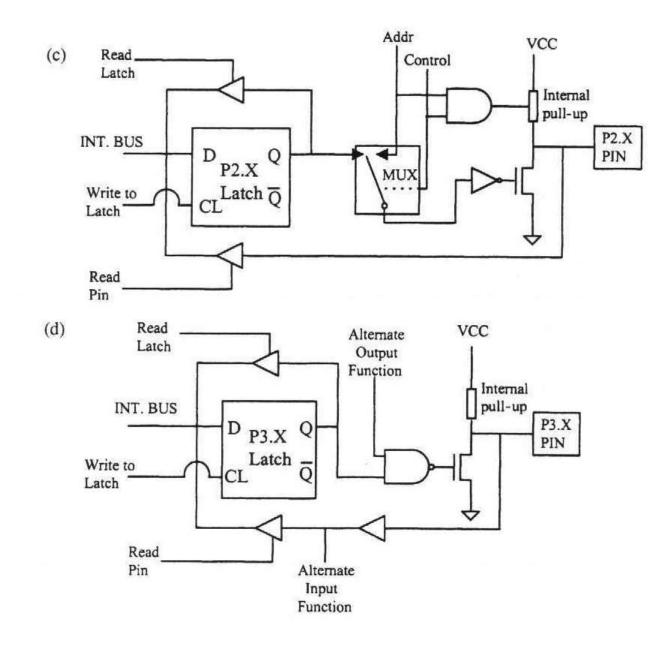

### A Pin of Port 1

Saturday, May 1, 2021

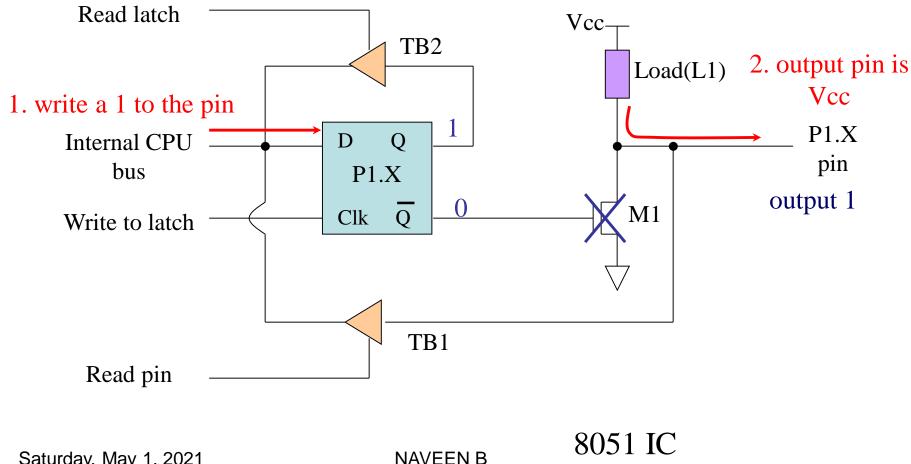

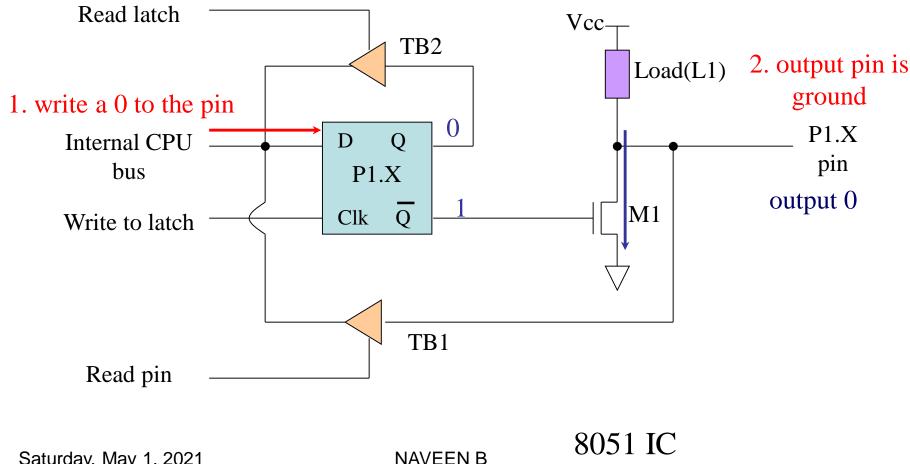

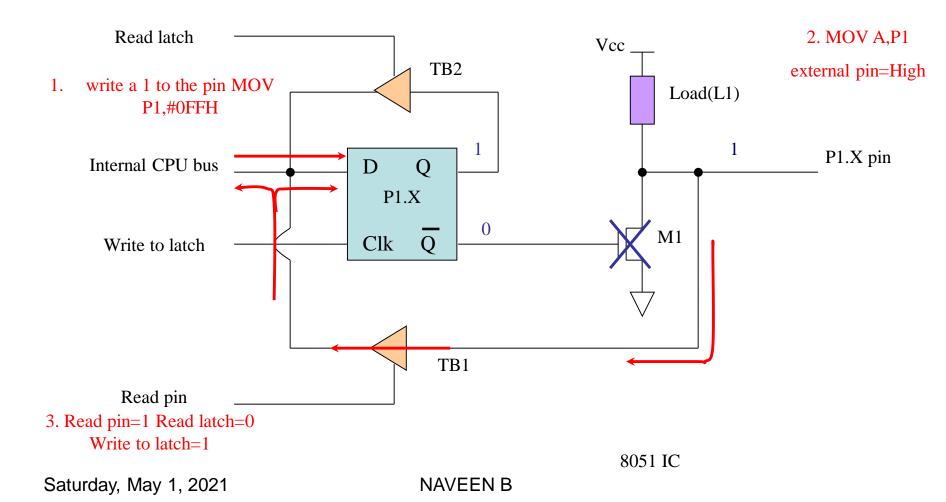

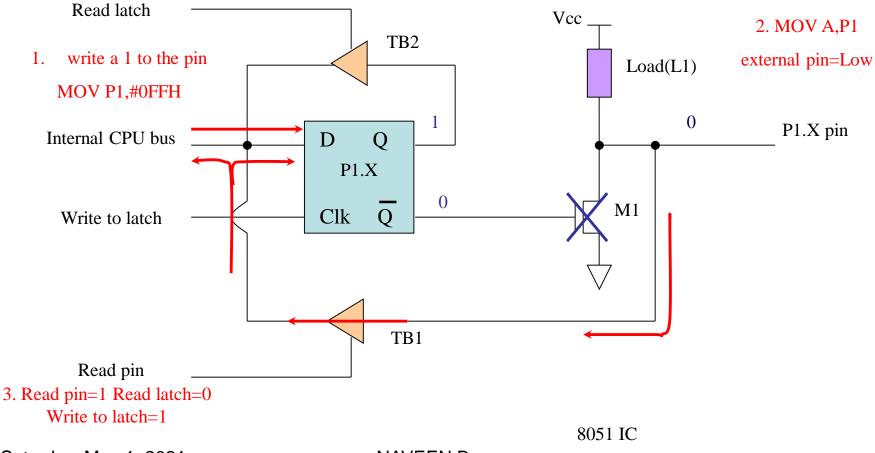

# Hardware Structure of I/O Pin

- Each pin of I/O ports

- Internal CPU bus : communicate with CPU

- A D latch store the value of this pin

- D latch is controlled by "Write to latch"

- Write to latch = 1: write data into the D latch

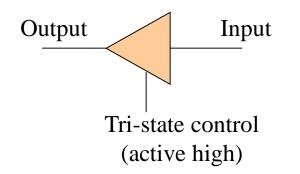

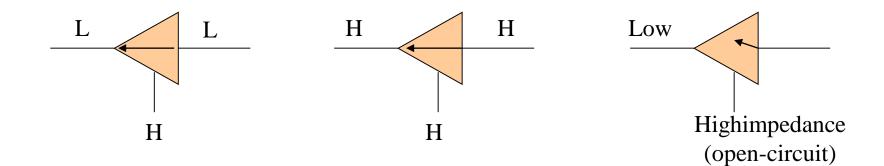

- − 2 Tri-state buffer : 🖬

- TB1: controlled by "Read pin"

- Read pin=1: really read the data present at the pin

- TB2: controlled by "Read latch"

- Read latch = 1 : read value from internal latch

- A transistor M1 gate

- Gate=0: open

- Gate=1: close Saturday, May 1, 2021

### Tri-state Buffer

# Writing "1" to Output Pin P1.X

Saturday, May 1, 2021

# Writing "0" to Output Pin P1.X

Saturday, May 1, 2021

### Port 1 as Output (Write to a Port)

• Send data to Port 1 :

MOV A,#55H BACK: MOV P1,A ACALL DELAY CPL A SJMP BACK

- Let P1 toggle.

- You can write to P1 directly.

Saturday, May 1, 2021

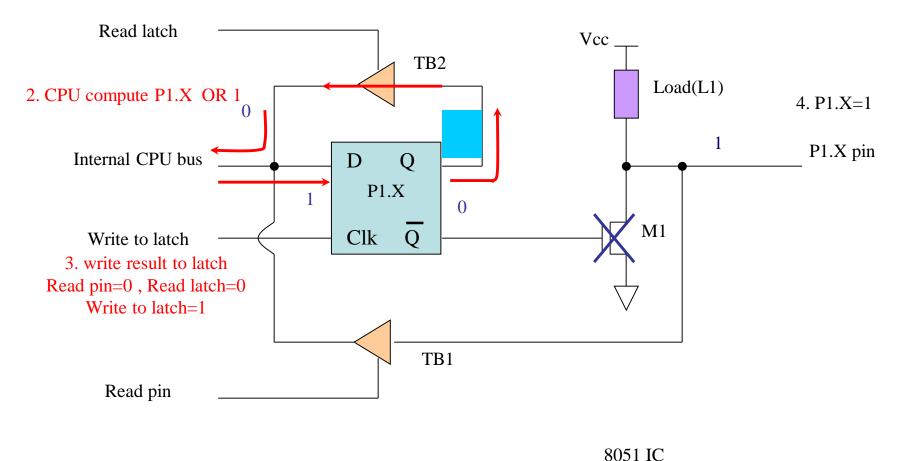

### Reading Input v.s. Port Latch

- When reading ports, there are two possibilities :

- Read the status of the input pin. (from *external pin value*)

- MOV A, PX

- JNB P2.1, TARGET ; jump if P2.1 is not set

- JB P2.1, TARGET ; jump if P2.1 is set

- Read the *internal latch* of the output port.

- ANL P1, A ; P1  $\leftarrow$  P1 AND A

- ORL P1, A ; P1  $\leftarrow$  P1 OR A

- INC P1 ; increase P1

### Reading "High" at Input Pin

### Reading "Low" at Input Pin

Saturday, May 1, 2021

# Port 1 as Input (Read from Port)

• In order to make P1 an input, the port must be programmed by writing 1 to all the bit.

|       | MOV  | A,#0FFH     | ;A=11111111B           |

|-------|------|-------------|------------------------|

|       | MOV  | <b>P1,A</b> | ;make P1 an input port |

| BACK: | MOV  | A,P0        | ;get data from P0      |

|       | MOV  | <b>P2,A</b> | ;send data to P2       |

|       | SJMP | BACK        |                        |

- To be an input port, P0, P1, P2 and P3 have similar methods.

### Instructions For Reading an Input Port

• Following are instructions for reading external pins of ports:

| Mnemonics  | Examples          | Description                      |

|------------|-------------------|----------------------------------|

| MOV A,PX   | MOVA,P2           | Bring into A the data at P2 pins |

| JNB PX.Y,  | JNB P2.1, TARGET  | Jump if pin P2.1 is low          |

| JB PX.Y,   | JB P1.3,TARGET    | Jump if pin P1.3 is high         |

| MOV C,PX.Y | <b>MOV C,P2.4</b> | Copy status of pin P2.4 to CY    |

### Reading Latch

• Exclusive-or the Port 1 :

MOV P1,#55H ;P1=01010101

ORL P1,#0F0H ;P1=11110101

- 1. The read latch activates TB2 and bring the data from the Q latch into CPU.

- Read P1.0=0

- 2. CPU performs an operation.

- This data is ORed with bit 1 of register A. Get 1.

- 3. The latch is modified.

- D latch of P1.0 has value 1.

- 4. The result is written to the external pin.

- External pin (pin 1: P1.0) has value 1.

Saturday, May 1, 2021

### Reading the Latch

1. Read pin=0 Read latch=1 Write to latch=0 (Assume P1.X=0 initially)

Saturday, May 1, 2021

### Read-modify-write Feature

- Read-modify-write Instructions

- This features combines 3 actions in a single instruction :

1. CPU reads the latch of the port

- 2. CPU perform the operation

- 3. Modifying the latch

- 4. Writing to the pin

- Note that 8 pins of P1 work independently.

#### Port 1 as Input (Read from latch)

• Exclusive-or the Port 1 :

MOV P1,#55H ;P1=01010101 AGAIN: XOR P1,#0FFH ;complement ACALL DELAY SJMP AGAIN

- Note that the XOR of 55H and FFH gives AAH.

- XOR of AAH and FFH gives 55H.

- The instruction read the data in the latch (not from the pin).

- The instruction result will put into the latch and the pin.

### **Read-Modify-Write Instructions**

| Example          |

|------------------|

| ANL P1,A         |

| ORL P1,A         |

| XRL P1,A         |

| JBC P1.1, TARGET |

| CPL P1.2         |

| INC P1           |

| DEC P1           |

| DJNZ P1,TARGET   |

| MOV P1.2,C       |

| CLR P1.3         |

| SETB P1.4        |

|                  |

Saturday, May 1, 2021

#### You are able to answer this Questions:

- How to write the data to a pin ?

- How to read the data from the pin?

- Read the value present at the external pin.

- Why we need to set the pin first ?

- Read the value come from the latch (not from the external pin).

- Why the instruction is called read-modify write?

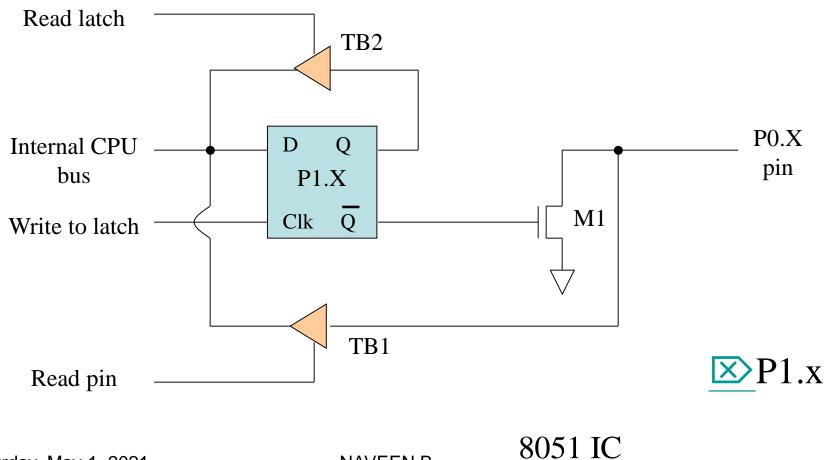

### Other Pins

• P1, P2, and P3 have internal pull-up resisters.

– P1, P2, and P3 are not open drain.

- P0 has no internal pull-up resistors and does not connects to Vcc inside the 8051.

- P0 is open drain.

- Compare the figures of P1.X and P0.X.

- However, for a programmer, it is the same to program P0, P1, P2 and P3.

- All the ports upon RESET are configured as output.

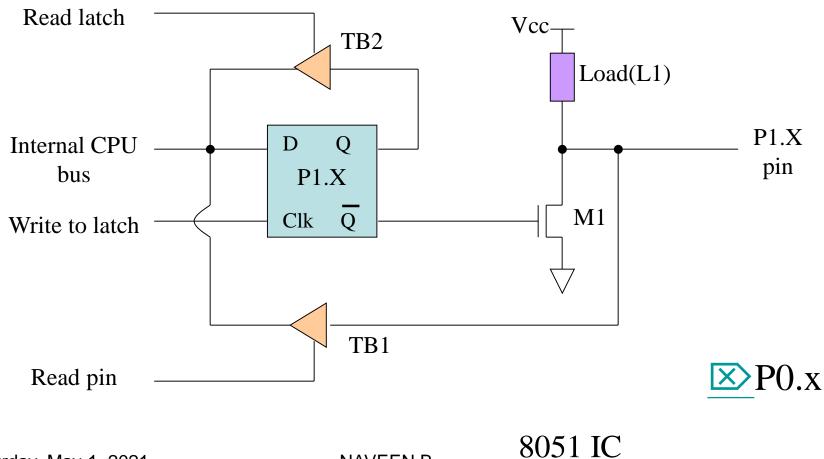

### A Pin of Port 0

Saturday, May 1, 2021

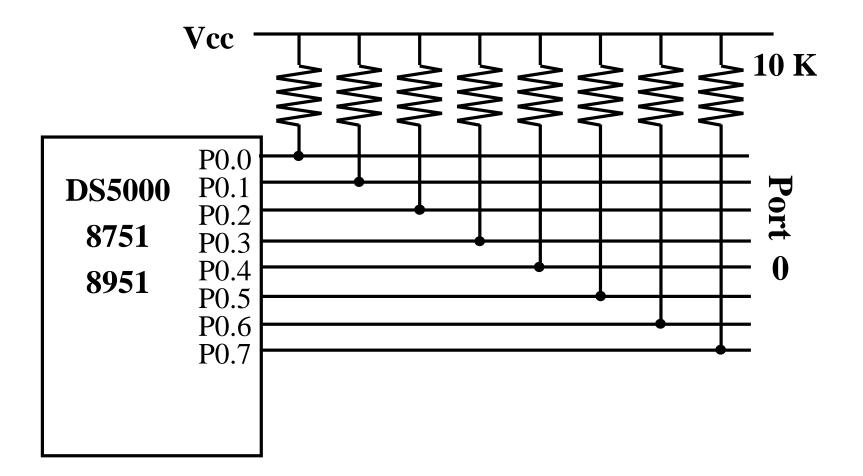

# Port 0 (pins 32-39)

- P0 is an open drain.

- Open drain is a term used for MOS chips in the same way that open collector is used for TTL chips.

- When P0 is used for simple data I/O we must connect it to external pull-up resistors.

- Each pin of P0 must be connected externally to a 10K ohm pull-up resistor.

- With external pull-up resistors connected upon reset, port 0 is configured as an output port.

### Port 0 with Pull-Up Resistors

Saturday, May 1, 2021

### Dual Role of Port 0

- When connecting an 8051 to an external memory, the 8051 uses ports to send addresses and read instructions.

- 8051 is capable of accessing 64K bytes of external memory.

- 16-bit address : P0 provides both address A0-A7, P2 provides address A8-A15.

- Also, P0 provides data lines D0-D7.

- When P0 is used for address/data multiplexing, it is connected to the 74LS373 to latch the address.

- There is no need for external pull-up resistors

Saturday, May 1, 2021

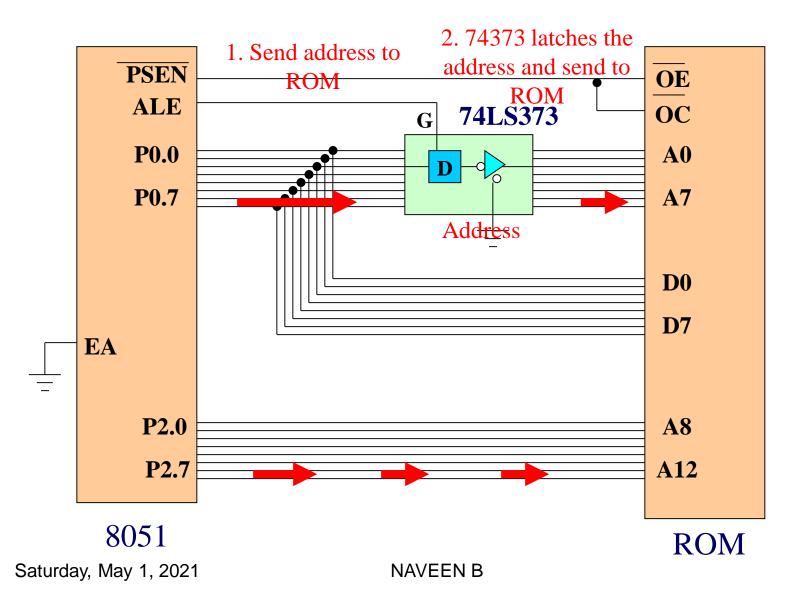

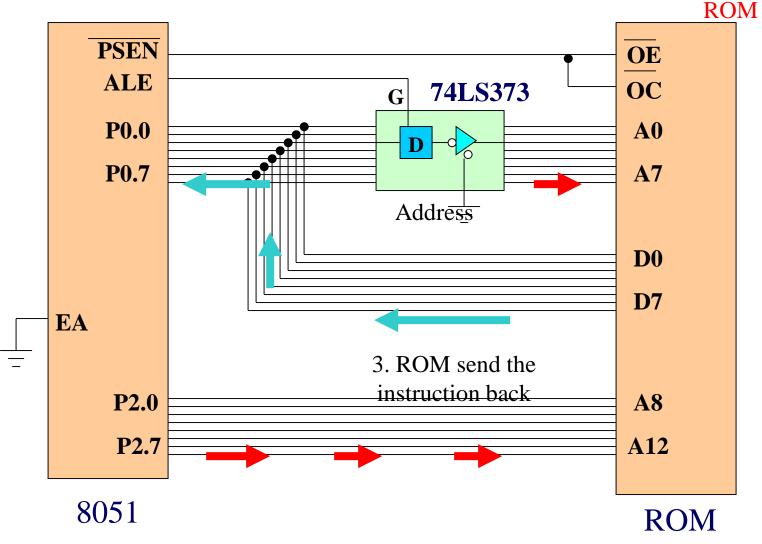

### Reading ROM (1/2)

Reading ROM (2/2) 2. 74373 latches the address and send to address and send to

Saturday, May 1, 2021

# ALE Pin

- The ALE pin is used for de-multiplexing the address and data by connecting to the G pin of the 74LS373 latch.

- When ALE=0, P0 provides data D0-D7.

- When ALE=1, P0 provides address A0-A7.

- The reason is to allow P0 to multiplex address and data.

# Port 2 (pins 21-28)

- Port 2 does not need any pull-up resistors since it already has pull-up resistors internally.

- In an 8051-based system, P2 are used to provide address A8-A15.

# Port 3 (pins 10-17)

- Port 3 does not need any pull-up resistors since it already has pull-up resistors internally.

- Although port 3 is configured as an output port upon reset, this is not the way it is most commonly used.

- Port 3 has the additional function of providing signals.

- Serial communications signal : RxD, TxD (Chapter 10)

- External interrupt : /INT0, /INT1 (Chapter 11)

- Timer/counter : T0, T1 (Chapter 9)

- External memory accesses in 8031-based system : /WR,

/RD (Chapter 14)

### Port 3 Alternate Functions

| P3 Bit | Function | Pin |

|--------|----------|-----|

|        |          |     |

| P3.0   | RxD      | 10  |

| P3.1   | TxD      | 11  |

| P3.2   | INT0     | 12  |

| P3.3   | INT1     | 13  |

| P3.4   | T0       | 14  |

| P3.5   | T1       | 15  |

| P3.6   | WR       | 16  |

| P3.7   | RD       | 17  |

|        |          |     |

Saturday, May 1, 2021

NAVEEN B

$\boxtimes$

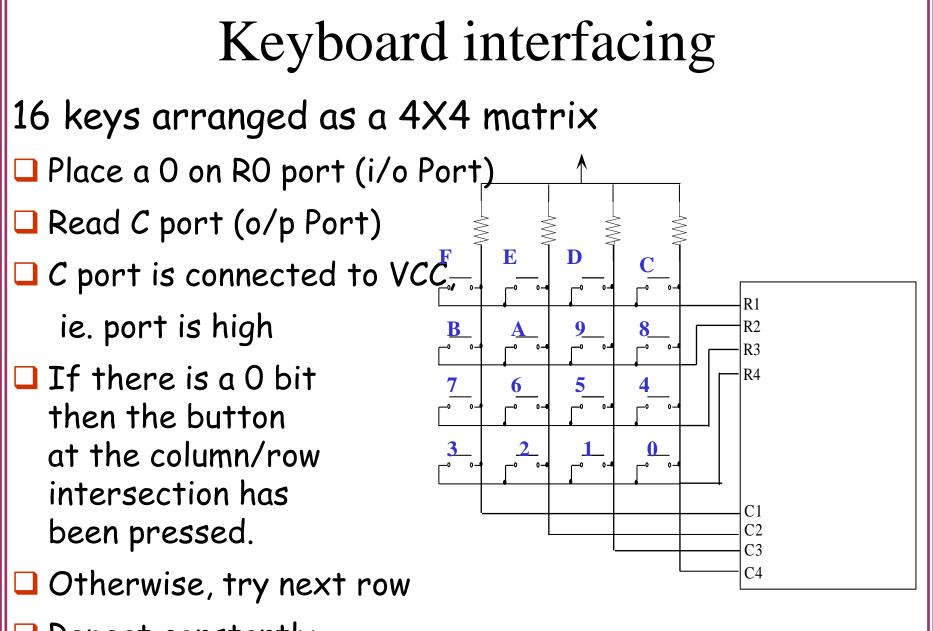

### Counters & timers

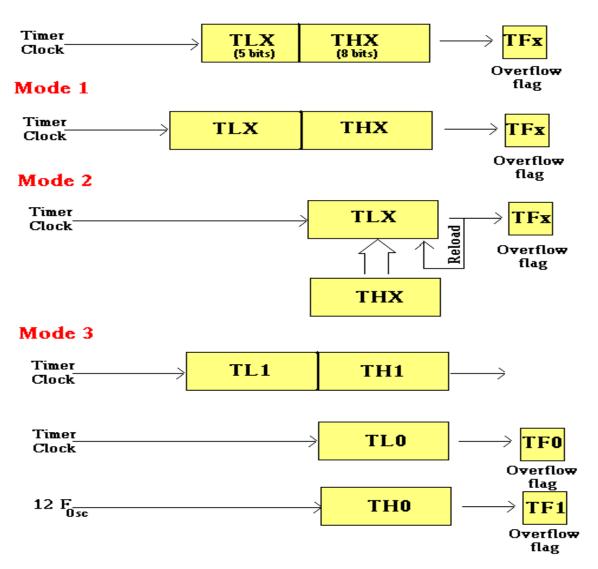

To relinquish the Burden of the processor from software loops for timing & counting, two 16 bit counters T0 & T1 are provided. These 2 are divided into 8 bit registers as timer low(TL0, TL1) and high(TH0, TH1) bytes. Counter action is controlled by timer mode control (TMOD) & timer/counter control reg. (TCON)

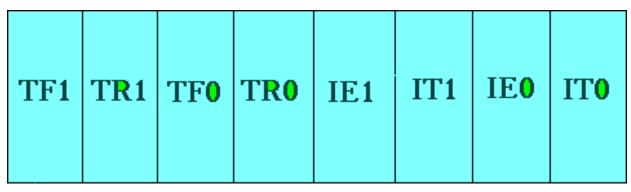

### **TCON Register:**

- TF1: Timer 1 overflow flag.

- TR1: Timer 1 run control bit.(set to 1 to enable timer to count)

- TF0: Timer 0 overflag.

- TR0: Timer 0 run control bit.

- IE1: External interrupt 1 edge flag.

- IT1: External interrupt 1 type flag.

- IE0: External interrupt 0 edge flag.

- ITO: External interrupt 0 type flag. Saturday, May 1, 2021 NABELEN B

### Timer mode control reg. (TMOD)

(Not bit addressable)

|   | (M                          | SB)                         |                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |            |                          | (LSB)    |

|---|-----------------------------|-----------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|--------------------------|----------|

|   |                             | GATE                        | C/T                                   | M1                                                                                               | M0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GATE                                        | C/T        | M1                       | M0       |

|   |                             |                             | Tir                                   | ner 1                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             | Tim        | ner 0                    |          |

|   | GATE                        | 20110-10-00                 | • • • • • • • • • • • • • • • • • • • |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | inter is enat                               |            |                          |          |

|   |                             |                             |                                       | Rx control<br>Rx control                                                                         | A CONTRACTOR OF A CONTRACTOR OFTA CONTRACTOR O | When clea                                   | red, the t | imer is en               | abled    |

|   | C/T                         |                             |                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | or timer ope<br>ation (input                |            |                          |          |

|   |                             |                             |                                       | 말라고 같이 많이 잘 다 안 가지지?                                                                             | 400 SH 68 DANAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1999 - 1997 - N. 199 <b>8</b> - 1997 - 1997 |            | 1000 A.C. 100 A.C. 10    |          |

|   | M1                          | Mode                        | bit 1                                 |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |            |                          |          |

| 1 | M1<br>M0                    | Mode<br>Mode                |                                       |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |            |                          |          |

|   | M0<br><u>M1</u>             |                             |                                       | Operating                                                                                        | g Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                             |            |                          |          |

|   |                             | Mode                        | bit 0                                 | 13-bit tim                                                                                       | ner mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |            |                          |          |

|   | M0<br><u>M1</u>             | Mode<br><u>M0</u>           | bit 0<br><u>Mode</u>                  | 13-bit time<br>8-bit time                                                                        | ner mode<br>er/counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | THx with 1                                  | TLx as 5-  | bit presca               | ler      |

|   | M0<br><u>M1</u>             | Mode<br><u>M0</u>           | bit 0<br><u>Mode</u>                  | 13-bit time<br>8-bit time<br>16-bit time                                                         | ner mode<br>er/counter<br>ner mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |            |                          |          |

|   | <b>M0</b><br><u>M1</u><br>0 | Mode<br><u>M0</u><br>0      | bit 0<br><u>Mode</u>                  | 13-bit time<br>8-bit time<br>16-bit time                                                         | ner mode<br>er/counter<br>ner mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | THx with <sup>*</sup><br>rs THx and         |            |                          |          |

|   | <b>M0</b><br><u>M1</u><br>0 | Mode<br><u>M0</u><br>0<br>1 | bit 0<br><u>Mode</u>                  | 13-bit time<br>8-bit time<br>16-bit time                                                         | her mode<br>er/counter<br>her mode<br>her/counte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |            |                          |          |

|   | <b>M0</b><br><u>M1</u><br>0 | Mode<br><u>M0</u><br>0      | bit 0<br><u>Mode</u>                  | 13-bit time<br>8-bit time<br>16-bit tim<br>16-bit tim                                            | her mode<br>er/counter<br>her mode<br>her/counte<br>lar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |            |                          |          |

|   | <b>M0</b><br><u>M1</u><br>0 | Mode<br><u>M0</u><br>0<br>1 | bit 0<br><u>Mode</u><br>0<br>1        | 13-bit time<br>8-bit time<br>16-bit time<br>16-bit time<br>no presca<br>8-bit auto<br>8-bit auto | her mode<br>er/counter<br>her mode<br>her/counte<br>lar<br>o reload<br>o reload tin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                             | TLx are    | cascaded;<br>olds a valu | there is |

### Gate = 0 : start & stop are software control (Start by SETB TRx & stop by CLR TRx) Gate = 1 : start & stop are controlled by hardware

by an external source (Pins P3.2 & P3.3)

#### Mode 0

#### Interrupt :

Program execution without intrrupts :

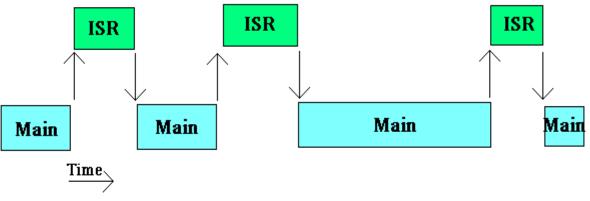

**Program execution with intrrupts :**

Saturday, May 1, 2021

NAVEEN B

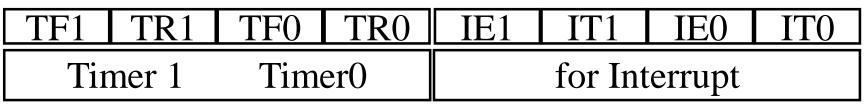

#### **Interrupt Vectors**

| Interrupt    | Vector Address |

|--------------|----------------|

| System Reset | <b>0000H</b>   |

| External 0   | 0003H          |

| Timer 0      | 000BH          |

| External 1   | 0013H          |

| Timer 1      | 001BH          |

| Serial Port  | 0023H          |

| Timer 2      | 002BH          |

#### Interrupt Enable Register :

# EA \_ ET2 'ES ET1 EX1 ET0 EX0

- EA : Global enable/disable.

- --- : Undefined.

- ET2 :Enable Timer 2 interrupt.

- ES :Enable Serial port interrupt.

- ET1 :Enable Timer 1 interrupt.

- EX1 :Enable External 1 interrupt.

- ET0 : Enable Timer 0 interrupt.

- EX0 : Enable External 0 interrupt.

#### Interrupt priority register

|     |        | PT2                                     | PS         | PT1         | PX1         | PT0 | PX0 |

|-----|--------|-----------------------------------------|------------|-------------|-------------|-----|-----|

|     |        |                                         |            |             |             |     |     |

| Bit | symbol | fu                                      | nction     |             |             |     |     |

| 7   |        | nc                                      | t impleme  | ented       |             |     |     |

| 6   |        | nc                                      | ot implem  | nented      |             |     |     |

| 5   | PT2    | re                                      | served fo  | or future u | JSE         |     |     |

| 4   | PS     | priority for serial port interrupt      |            |             |             |     |     |

| 3   | PT1    | priority for timer 1 overflow interrupt |            |             |             |     |     |

| 2   | PX1    | priority for external interrupt 1       |            |             |             |     |     |

| 1   | PT0    | priority for timer 0 overflow interrupt |            |             |             |     |     |

| 0   | PX0    | pr                                      | iority for | external i  | interrupt ( | C   |     |

IP=0 (low priority) Saturday, May 1, 2021 IP=1 (High priority)

NAVEEN B

#### Interrupt priority

- If the 2 interrupts with the same priority occur at the same time, then they have the following ranking-

- IE0, TF0, IE1, TF1, Serial interrupt (RI or TI)

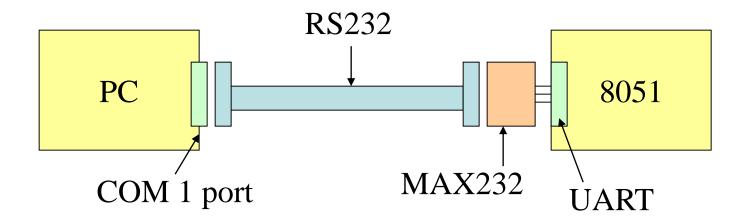

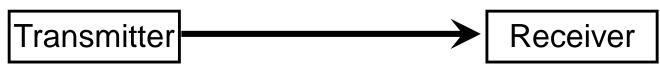

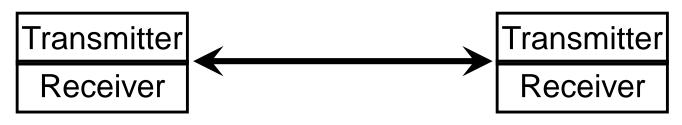

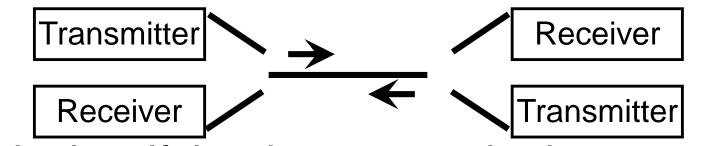

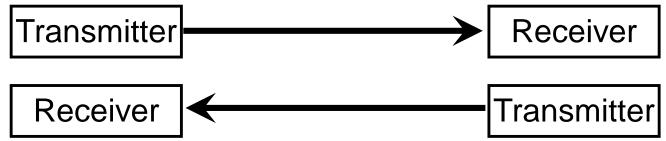

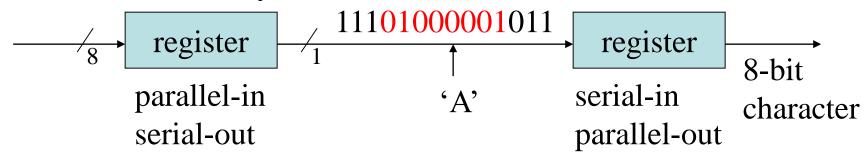

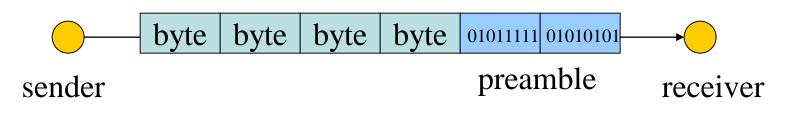

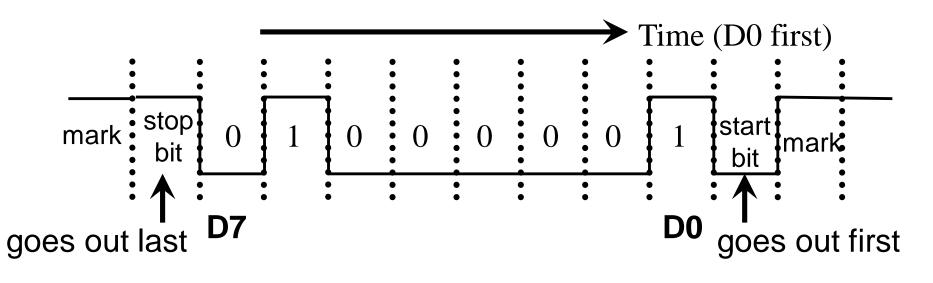

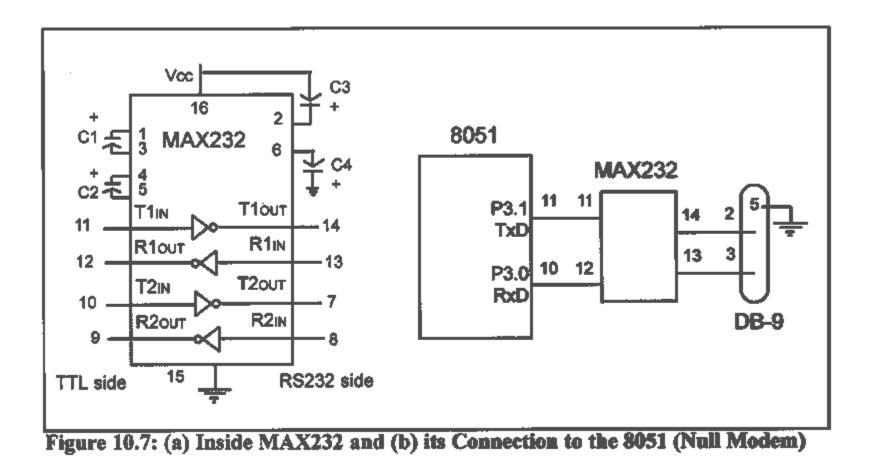

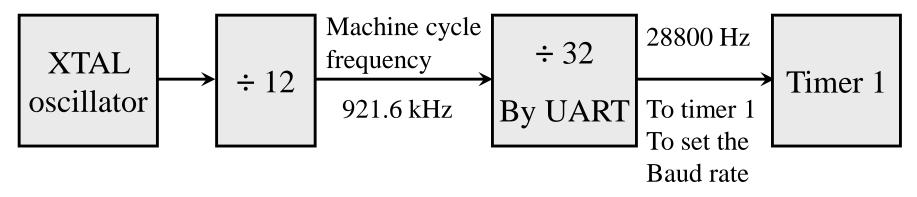

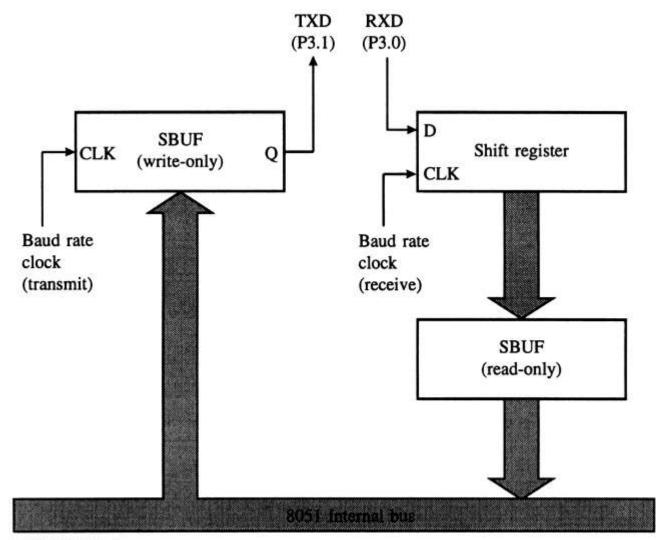

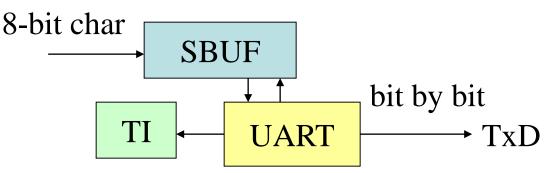

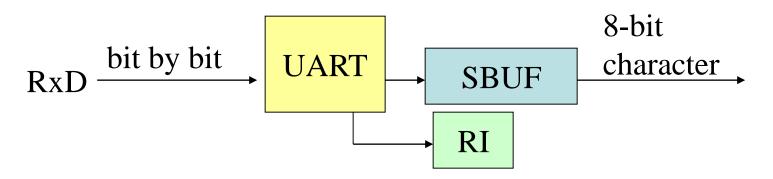

#### Serial data I/O

- 8051 has a full duplex serial port

- SBUF to hold data, SCON controls data communication and PCON controls data rates

- SBUF is physically 2 regs., one is to hold write only data and another is read only data

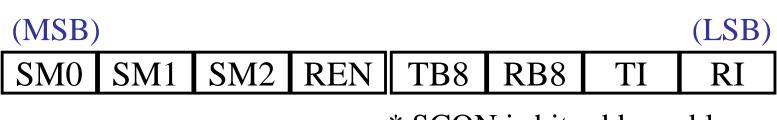

#### Serial port control (SCON)

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

|-----|-----|-----|-----|-----|-----|----|----|

|-----|-----|-----|-----|-----|-----|----|----|

| <u>Bit</u>            | <u>symbol</u> | <u>function</u>           |  |  |

|-----------------------|---------------|---------------------------|--|--|

| 7                     | SM0           | serial port mode bit 0    |  |  |

| 6                     | SM1           | serial port mode bit 1    |  |  |

| 5                     | SM2           | multiprocessor commn. Bit |  |  |

| 4                     | REN           | receive enable bit        |  |  |

| 3                     | TB8           | transmitted bit 8         |  |  |

| 2                     | RB8           | received bit 8            |  |  |

| 1                     | TI            | transmit interrupt flag   |  |  |

| 0                     | RI            | receive interrupt flag    |  |  |

| Saturday, May 1, 2021 |               | NAVEEN B                  |  |  |

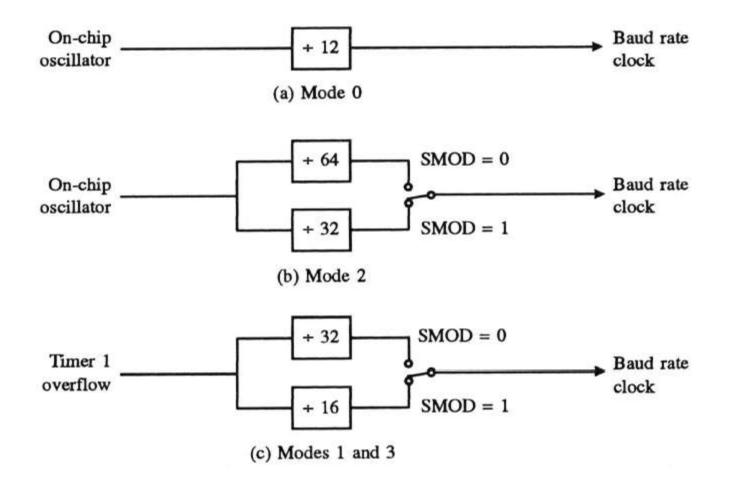

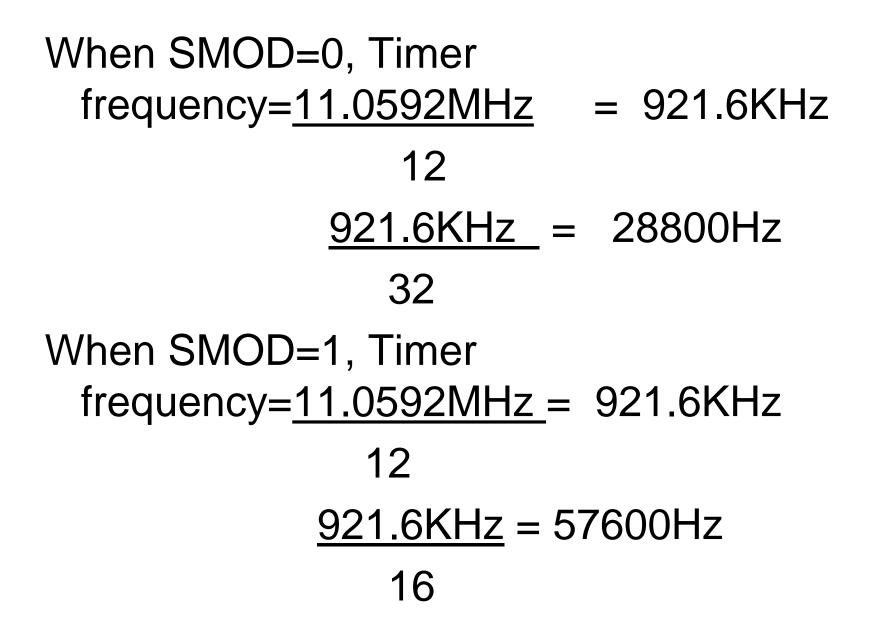

There are 4 programmable modes for serial data commn.

| SM0 | SM1 | Mode | Description                   |

|-----|-----|------|-------------------------------|

| 0   | 0   | 0    | shift register; baud=f/12     |

| 0   | 1   | 1    | 8-bit UART; baud=variable     |

| 1   | 0   | 2    | 9-bit UART; baud=f/32 or f/64 |

| 1   | 1   | 3    | 9-bit UART; baud=variable     |

Mode 0 (shift register mode) : SBUF to transmit/receive 8 data bits using pin RXD for both functions. TXD is used to supply shift pulses to external circuits. Baud rate is fixed at f/12. Mode 1 (standard UART): SBUF becomes a 10-bit full duplex receiver/transmitter at the same time using RXD & TXD.

1 start bit, 8 data bits (LSB first) & 1 stop bit. 8 data bits go to SBUF, start bit is discarded & stop bit is saved in RB8.

Mode 2 (multiprocessor mode): similar to mode1 except 11 bits are transmitted (9 data bits). 9<sup>th</sup> bit is copied from bit TB8 during transmit & stored in bit RB8 when data is received. Both start & stop bits are discarded.

For multiprocessor commn., set the 9<sup>th</sup> data bit.

Mode 3 (serial data mode): this is identical to mode 2 except that the baud rate is as in mode 1, using timer 1 to generate frequencies. Saturday, May 1, 2021 NAVEEN B

#### PC variable Baud Rates

| 110 bps        |  |

|----------------|--|

| 150            |  |

| 300            |  |

| 600            |  |

| 1200           |  |

| 2400           |  |

| 4800           |  |

| 9600 (default) |  |

| 19200          |  |

#### Power mode control (PCON)

| SMOD       |              | -          | -                           | GF1     | GF0    | PD       | IDL      |  |

|------------|--------------|------------|-----------------------------|---------|--------|----------|----------|--|

| <u>Bit</u> | <u>sym</u> t | <u>loc</u> | <u>fu</u>                   | Inction |        |          |          |  |

| 7          | SMO          | DD         | serial baud rate modify bit |         |        |          |          |  |

| 6-4        |              |            | not implemented             |         |        |          |          |  |

| 3          | GF           | 1          | gene                        | ral pur | pose ι | iser fla | ig bit 1 |  |

| 2          | GF           | О          | gene                        | ral pur | pose ι | iser fla | ng bit 0 |  |

| 1          | PD           | )          | power down bit              |         |        |          |          |  |

| 0          | ID           | L          | ideal mode bit              |         |        |          |          |  |

• This is not bit addressable Saturday, May 1, 2021

#### 8051Instruction Set By Dr. Naveen B

#### **Instruction Set**

**Data Transfer Instructions**

MOVE Destination, Source

MOV Rn, A

MOV Rn, direct

MOV DPTR, # data 16 MOVC A, @ A + DPTR MOVC A, @ A+PC

MOVX A, @DPTR MOVX @DPTR, A MOVX A, @Ri

\*\* No flags are affected

#### **Logical Operations** Byte level Logical operations

The operations are done in each individual bit of the source & destination bytes.

- ANL A, Rn ORLA, @Rp XRL A, #27h Destination is Accumulator or direct addressing & source may be any addressing mode. Use port as a source but not as a destination • CLR A Clear Acc CPL A Complement Acc

- \*\* No flags are affected

#### **Bit level Logical Operations**

• It is very convenient to alter a single bit of a byte.

#### CPL C (Complement)

- CPL bit

- ANL C, bit AND direct bit to CY

- ANL C, /bit

- ORL C, bit

- ORL C, /bit

#### EX:SETB 00h ...Bit 0 of RAM byte 20h = 1 ANL C, /00h ...C=0; bit 0 of RAM byte 20h =1

|       |         | <b>BOOLEAN OPERATIONS</b>                                            |

|-------|---------|----------------------------------------------------------------------|

| CLR   | C       | Clear CY                                                             |

| CLR   | bit     | Clear direct bit                                                     |

| SETB  | С       | Set CY                                                               |

| SETB  | bit     | Set direct bit (SETB P2.4)                                           |

| MOV   | C, bit  | Move direct bit to CY                                                |

| MOV   | bit, C  | Move CY to direct bit                                                |

| MOV   | 7Fh, C  | Bit 7 of RAM byte 2Fh =1Assume C=1                                   |

| Note: |         |                                                                      |

| • CLF |         | is for byte & only 'A' reg. no other<br>egisters or addressing modes |

| CLR A | cc.0 fo | or individual bit in 'A' reg.                                        |

| CLR b | bits in | SFRs & bit addressable area.                                         |

#### **Rotate and Swap Operations**

RL ARotate Acc Left:  $b_{n+1} \leftarrow b_n$ RR ARotate Acc Right:  $b_n \leftarrow b_{n+1}$ RLC ARotate Acc Left through Carry

RRC A Rotate Acc Right through Carry

SWAP A Exchange between the nibbles

\* Only CY flag is affected in RRC A & RLC A

#### **Example programs:**

1) **Double the number in Reg. R2 & put the result in R3 & R4.**

CLR C MOV A, R2 RLC A MOV R4, A CLR A RLC A MOV R3, A

2) OR the contents of ports 1 & 2, put the result in external RAM location 0100h

MOV A, 90h ORL A, 0A0h MOV DPTR, #0100h MOVX @DPTR, A 3) Configure P1 to read switches at P1.0 & P1.1. If P1.0 is high, turn ON a relay connected to P2.5 by sending a logic high o/p. If P1.0 is low, clear P2.5. If the status of the switch at P1.1 is high, turn OFF the relay connected to P2.6 by sending a logic low o/p. If P1.1 is low, set P2.6 to high state.

> Logic: <u>i/p's at P1</u> XXXXXX00 XXXXXX01 XXXXXX10 XXXXXX10

<u>o/p's at P2</u> X10XXXX X11XXXX X00XXXXX X01XXXX

#### Program:

mov p1, #0FFh Mov p2, #00h Mov A, p1 Anl A, #03h Cpl Acc.1 **RI**a **RI**a **RI**a **RI** a **RI**a Mov p2, A

4) Swap every even numbered bit of register R3 in bank 0 woth the odd numbered bit to its left. Swap bit 0 with bit 1, bit 2 with bit 3, and so on until bit 6 is swapped with bit 7

MOV A, R3 RL A ANL A, #0AAh PUSH 0E0h MOV A, R3 RR A ANL A, #55h MOV R3, A POP 0E0h ORL 03h, A (ORL

(ORL R3, A .... Not allowed)

5. Assume that bit P2.2 is used to control an outdoor light and bit P2.5 a light inside a building .Show how to turn on the outside light & turn off the inside one. SETB C **ORL C, P2.2** mov P2.2, C **CLR** C **ANL C, P2.5** mov P2.5 ,C

6. Assume that registers A has packed BCD. Write a pgm to convert packed BCD to two ASCII numbers & place them in R2 & R6.

mov A, # 29h mov R2, A ANL A, # 0Fh **ORL A, #30h** mov R6, A mov A, R2 **ANL A, # 0F0h** RRA RRA RRA RRA **ORL A, # 30h** mov R2, A

**Arithmetic Instructions** Incrementing and decrementing

INC A ; operand may be any addressing except Immediate

INC DPTR

DEC A :operand may be any addressing except Immediate There is no "DEC DPTR"

No flags are affected

#### Addition and subtraction:

ADD A, Source byte [OV, AC, CY]

ADDC A, Source byte [OV, AC, CY]

SUBB A, source byte [OV, AC, CY]

#### **Subtract with borrow:**

(A) ← (A) - source byte -CY

'A' register is the destination, & source may be any addressing mode

#### Examples

**Unsigned addition:** This make use of the carry flag to detect when the result of an ADD operation is a number larger than FF h.

| /        | 00 to 255d          |              |

|----------|---------------------|--------------|

| 95d =    | = 01011111 b        | =5Fh         |

| <br>189d | = <u>10111101 b</u> | = <u>BDh</u> |

| 284d     | 100011100 b         | 11Ch         |

|          |                     |              |

Signed addition: If unlike signed numbers are added, then it is not possible for the result to be larger than -128 d to +127 d, and the result will always be correct.

| Ex1: -001d = 11111111b                  | = FF h       |

|-----------------------------------------|--------------|

| +027d = 00011011 b                      | <u>= 1Bh</u> |

| <u>+026d</u> <u>100011010 b</u> =+ 026d | 11Ah         |

| Addin  | two two      | pumbara requit may avoad   | 1204       |                      |

|--------|--------------|----------------------------|------------|----------------------|

| Adding |              | numbers, result may exceed | +1280      |                      |

| Ex2:   | +100d        | =01100100b                 | =64h       |                      |

| /      | <u>+050d</u> | = <u>00110010b</u>         | <u>32h</u> |                      |

|        | 150d         | 010010110b = -106d         | 096h       | correct result= +22d |

|        |              |                            | 0\         | /=1                  |

|        |              |                            |            |                      |

| Ex3: | +045d | =00101101b       | =2Dh |                            |

|------|-------|------------------|------|----------------------------|

| 1    | +075d | =01001011b       | =4Bh |                            |

|      | +120d | 001111000b =120d | 078h | OV=0 (result not exceeded) |

The result of adding two -ve numbers together for a sum that does not exceed the -ve limit.

| Ex: | - 030d        | = 11100010b      | = E2h        |

|-----|---------------|------------------|--------------|

|     | <u>- 050d</u> | <u>11001110b</u> | = <u>CEh</u> |